ノベラスシステムズ( NSADAQ:NVLS、以下、ノベラス)、本日、シリコン貫通ビア(TSV) パッケージング市場に向けて、Cu バリア/シード層用の新しいPVDプロセスを開発したと発表しました。このプロセスは、ノベラスが特許を持つHollow Cathode Magnetron(HCM)技術を用いた信頼性の高いINOVAプラットフォームを使用し、TSVアプリケーションに使われる従来のプロセスよりも4倍薄く、高いコンフォーマル性を有するCuシードを成膜することができます。このHCM TSV プロセスは、優れたサイドウォールとボトムカバレッジ、さらに次工程のTSV電解めっき工程においてもボイドフリーを実現しています。

2次元のpinを使用したチップパッケージングに対して、TSVでは複数のチップが互いの上に実装され、スペースを削減する3次元モジュールと呼ばれるパッケージングが可能となります。3次元実装されたチップは、互いに短いTSV銅配線で接続される為、デバイス速度の増加と低消費電力化が実現できます。またTSVによる3次元パッケージングは、小型化が進む携帯型家電製品に対して重要な要素である、高密度多機能性、およびより小さな実装面積を実現します。

TSV Cu配線は、チップ間を接続するピラーを形成する為に、PVD Cuバリア/シードに続いてCuの電解めっき埋め込みを行う、ダマシン成膜シーケンスを利用します。従来のデュアルダマシンのCu配線構造と比較すると、TSV構造では埋め込み箇所が深く、場合によっては200μmを超える場合もあります。高いアスペクト比をもつ構造は、コンフォーマルなシード層の成膜を困難にします。コンフォーマルではないCuシード層は、サイドウォールカバレッジ性能が悪いため、CuによるTSV埋め込みステップでボイドを発生させ、直接的にデバイス信頼性に影響を与えます。これまでは、このような問題に対してTSVのインテグレーション変更を行うことで対処してきました。一つの方法は、TSVのエッチングプロセスによって、垂直ではないサイドウォール、つまりテーパー形状のViasを形成し、アスペクト比を緩和することです。この結果、PVDのステップカバレッジは改善しますが、一方でパッケージング密度に制限を与えてしまいます。またもう一つの方法は、TSV構造にて十分なサイドウォールカバレッジを実現できるほどの、厚いCuシード膜を成膜することです。ですがこの方法では、消耗品コスト増加とシステムスループットの低下を招き、高価な製造プロセスになってしまいます。

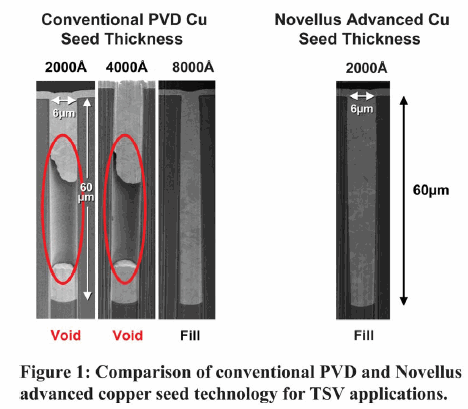

ノベラスの技術者は、従来の方法で直面した技術的な課題と高い生産コストの両方に対処するため、TSV実用化に向けてHCMを使ったCuバリア/シード層用のプロセスを開発しました。この革新的な技術では、PVDプロセスチャンバー内に強い局所的なイオン場を作るため、ノベラスが特許をもつ永久磁石リングを使用し、TSV構造のサイドウォール表面のイオン密度を増加させることが可能になります。この領域でのイオン密度の増加により、サイドウォールに付着するスパッタ膜粒子を増加させ、よりコンフォーマルな成膜を実現します。この高いコンフォーマル性能をもつプロセスは、テーパー形状サイドウォールの必要性を無くし、TSVアプリケーションに使われてきた典型的なPVDシード層よりも4倍薄いシード膜厚を可能とします。<図1>には、ノベラスのAdvanced Seedプロセスが、深さ60μm、10対1のアスペクト比、垂直なサイドウォール形状を持つTSV構造において、2000Å(オングストローム)の薄いCuシード膜を使って、ボイドフリーの埋め込みを実現したことを示しています。通常のPVD手法で同じ結果を得るには8000Å(オングストローム)のシード膜が必要です。この4倍も薄いTSVシード膜の実現は、通常のPVD手法と比較して、システムスループットにも多大な増加をもたらし、50%以上のCoCを削減することにつながっています。

ノベラスの半導体システム製品担当執行副社長のFusen Chenは次のように述べています。「TSV3次元技術は、将来の半導体パッケージングアプリケーションに対して非常に有望であり、技術面と生産面の両者の問題を克服することも可能と考えています。ノベラスの新しいAdvanced Seedプロセスは、TSVインテグレーションにおいて、これら両方の問題に対処でき、結果として、薄く、非常にコンフォーマルな膜を実現し、さらにメガファブのニーズを満たす優れたスループットをももたらすでしょう。」

ノベラスのPVD Cuバリア/シードテクノロジーについて:Cuバリア/シードアプリケーションに対して、特許を有するHollow Cathode Magnetron(HCM) INOXソーステクノロジーを特徴とするノベラスのINOVA(r) NExT PVDシステムは、2Xnmテクノロジーおよびそれ以降のテクノロジーノードへPVD技術を持続できる、優れたコンフォーマルバリア膜とシード層を提供します。

Novellus Systems, Inc. (Nasdaq: NVLS) は、グローバル半導体産業において先進のプロセスを提案するリーディングカンパニーです。ノベラスの製品は、信頼された生産性に裏付けされた革新的なテクノロジーを提供することにより、お客様に“価値”を提供します。S&P 500 companyであるノベラスは、米国カリフォルニア州サンノゼに本社をもち、世界中に拠点を展開しています。ノベラスについての詳細は公式サイトをご覧下さい。

http://www.novellus.co.jp| 2010-08-24 08:00:00 | ノベラスシステムズジャパン ノベラスがSUB-32nm FEOLおよびダブルパターニングアプリケーション向けにコンフォーマル成膜技術を発表 VECTOR(R)プラットホームにてFurnaceの膜質クオリティとALDに匹敵するステップカバレッジ性能をもつ絶縁膜の実現 |

| 2010-05-18 11:00:00 | ノベラスシステムズジャパン ノベラスの新しいタングステンナイトライド(WN)プロセスが3xnm以降のメモリーデバイスの最先端銅配線を可能に ALTUS(R) DirectFill(TM) Liner-Barrierテクノロジーにてコンタクト抵抗30%低減を実現 |

| 2010-03-23 14:00:00 | ノベラスシステムズジャパン ノベラス、シリコン貫通ビア(TSV)パッケージに向け最先端Cuシードテクノロジーを開発 高アスペクト比のTSV構造において、新しいPVD HCM(r)プロセスがボイドフリーのCu埋め込みを実現 |

| 2010-03-04 12:00:00 | ノベラスシステムズジャパン ノベラスシステムズ、IBMおよびCNSEがAlbany NanoTech Complexにおける戦略的提携に合意 最初の目標は最先端のフォトレジスト除去技術の開発 |

| 2010-02-16 13:00:00 | ノベラスシステムズジャパン ノベラスシステムズ PECVD装置 VECTOR(R) 出荷数1000台を達成 GLOBALFOUNDRIESに認められた、業界をリードする量産対応絶縁膜成膜装置 |

| 2010-01-29 00:00:00 | ノベラスシステムズジャパン ノベラスシステムズ SUB-45nm大量生産向けSOLA(r) xT UVTP装置をリリース 柔軟性の高いMulti-station Sequential Processing (MSSP)によりULK膜硬度を25%改善 |

| 2009-12-08 00:00:00 | ノベラスシステムズジャパン ノベラスのPECVD ASHABLE HARD MASK (AHM(tm))がSub-32nmのパターニングを実現 従来のアモルファスカーボン膜に比べ歩留まりを7%改善 |