ノベラスシステムズ( NSADAQ:NVLS、以下、ノベラス)は、本日高度なメモリーデバイス向けである銅配線からタングステンViaへのアプリケーションとして、既存のPVDによるTiライナー膜とMO-CVDによるTiN膜のスタック構造に置き換わる革新的なDirectFill CVDタングステンナイトライド(WN)を開発したことを発表しました。WN膜は、最先端のPNLテクノロジーとMSSDアーキテクチャを用いたノベラスのAltusプラットフォームにより成膜されます。DirectFillプロセスは、既存のPVD Ti膜とMO-CVD TiN膜のスタック構造である200A厚の膜に比べ、より良いBarrier性と抵抗特性を持つ非常に薄い20AのWN膜を成膜します。この薄膜は、タングステンViaの抵抗を最大30%低減させ、Viaプロセスを3xnm、またそれ以降のテクノロジーノードへ延伸させます。

高速かつ低電力で将来への微細化の必要性がメモリーデバイスに高まったことが、DRAMとFlashに銅配線を用いる原動力となりました。通常使われるインテグレーションとしては、最初のメタル層に対して銅配線を、その後の層に対しては従来のアルミ配線を用います。このインテグレーションでは、アルミ配線と銅配線の導通のためにタングステンVia使うことが要求されます。また3xnmテクノロジーノードからの微細化に対し、既存のTi/TiNライナー・バリアスタック構造のタングステンViaプロセスにおいて、インテグレーションとスケーリングに関する新たな課題が発生しています。PVD Tiライナー膜のオーバーハングがViaの開口径を減少させ、CVDタングステンのViaの埋め込み不良を引き起こし、Viaセンター部にボイドを生じさせます。MO-CVDによるTiN成膜では、タングステンプラグ埋め込みプロセス中に用いるシランガスが、バリア内に拡散しViaのインターフェース上に高抵抗の銅シリサイドを発生させるのを防ぐため、薄膜が必要になります。TiNバリア性の劣化は、Tiライナー膜へタングステン・ヘキサフロライドによるアタックを生じさせ、Volcanoディフェクトを引き起こします。これらPVD TiとMO-CVD TiNのインテグレーションの諸問題は、高抵抗なVia、電気的特性の劣化、デバイス信頼性の低下を発生させます。

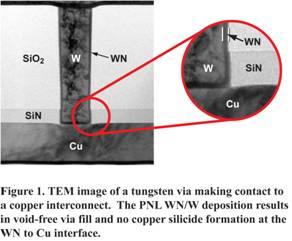

ノベラスのエンジニアは、既存のPVD TiとMO-CVD TiN膜の積層構造に置き換わる単層のDirectFill PNL WNライナー・バリア膜を開発することによって、これら諸問題を解決しました。PNL WNプロセステクノロジーは、非常に低抵抗なディフュージョンバリアとなるmicro-crystalline構造を持った、コンフォーマルな20Å厚のバリア層を成膜します。このコンフォ-マル性能は、ステップカバレッジとその後の従来のライナー・バリアテクノロジーを用いることに起因する埋め込みの問題を無くします。またこの膜構造が、Volcanoディフェクトや銅シリサイド化の原因となるディフージョンバリア性の劣化を防ぎます。図1は銅配線とタングステンViaコンタクトのTEM画像で、WN膜はバリア層として使われています。TEM画像からは、コンフォ-マルなWN膜が、ボイドフリーな埋め込みおよび銅配線とW/WN Viaプラグの間のきれいな界面を実現していることが分かります。更にこの非常に薄くコンフォーマルなWN層により、従来のPVD TiとMO-CVD TiNによるライナー・バリアスタック構造と比較して、最大30%Via抵抗が下がります。またノベラス特有のMSSDプロセスが、業界内で最高の生産性を提供します。

ノベラスのDirect Metals事業部副社長補佐兼統括部長であるAaron Fellis氏は次のように述べています。「DirectFill WNテクノロジーは、メモリーアプリケーション対して、従来のPVD TiとMO-CVD TiNによるライナー・バリア膜がもつインテグレーションの諸問題を解決し、最先端のタングステンバリア膜をお客様にご提供します。この新しいWN膜の優れたステップカバレッジとインテグレーション性能は、現在お客様がもつ銅配線構造に、3xnmテクノロジーノードとそれ以降への拡張性を提供します。」

ノベラスのALTUSタングステン成膜テクノロジーについて:1991年に導入されたALTUSは、タングステン成膜装置として実績のあるCVD装置であり、コンタクトとローカル配線アプリケーションに対し、高生産性と最先端のテクノロジーを提供します。

ALTUS Pulsed Nucleation Layer(PNL(R))はバルクCVDプロセスと高スループットのAtomic Layer Deposition(ALD)核生成プロセスを融合させたテクノロジーです。ノベラスの“Multi Station Sequential Deposition(MSSD)”アーキテクチャーは、核形成層とCVD埋め込みを同一のALTUSチャンバー内、個別のステーション上で連続成膜を可能としています。2008年に導入されたALTUS Maxは、信頼性とスループットを向上させ、生産性を25%改善しています。ALTUS Maxは業界ベンチマークの生産性と生産稼働率を達成し、業界内で最も低いCoO(Cost Of Ownership)を提供するタングステン装置です。

Novellus Systems, Inc. (Nasdaq: NVLS) は、グローバル半導体産業において先進のプロセスを提案するリーディングカンパニーです。ノベラスの製品は、信頼された生産性に裏付けされた革新的なテクノロジーを提供することにより、お客様に“価値”を提供します。S&P 500 companyであるノベラスは、米国カリフォルニア州サンノゼに本社をもち、世界中に拠点を展開しています。ノベラスについての詳細は公式サイトをご覧下さい。

http://www.novellus.co.jp| 2010-08-24 08:00:00 | ノベラスシステムズジャパン ノベラスがSUB-32nm FEOLおよびダブルパターニングアプリケーション向けにコンフォーマル成膜技術を発表 VECTOR(R)プラットホームにてFurnaceの膜質クオリティとALDに匹敵するステップカバレッジ性能をもつ絶縁膜の実現 |

| 2010-05-18 11:00:00 | ノベラスシステムズジャパン ノベラスの新しいタングステンナイトライド(WN)プロセスが3xnm以降のメモリーデバイスの最先端銅配線を可能に ALTUS(R) DirectFill(TM) Liner-Barrierテクノロジーにてコンタクト抵抗30%低減を実現 |

| 2010-03-23 14:00:00 | ノベラスシステムズジャパン ノベラス、シリコン貫通ビア(TSV)パッケージに向け最先端Cuシードテクノロジーを開発 高アスペクト比のTSV構造において、新しいPVD HCM(r)プロセスがボイドフリーのCu埋め込みを実現 |

| 2010-03-04 12:00:00 | ノベラスシステムズジャパン ノベラスシステムズ、IBMおよびCNSEがAlbany NanoTech Complexにおける戦略的提携に合意 最初の目標は最先端のフォトレジスト除去技術の開発 |

| 2010-02-16 13:00:00 | ノベラスシステムズジャパン ノベラスシステムズ PECVD装置 VECTOR(R) 出荷数1000台を達成 GLOBALFOUNDRIESに認められた、業界をリードする量産対応絶縁膜成膜装置 |

| 2010-01-29 00:00:00 | ノベラスシステムズジャパン ノベラスシステムズ SUB-45nm大量生産向けSOLA(r) xT UVTP装置をリリース 柔軟性の高いMulti-station Sequential Processing (MSSP)によりULK膜硬度を25%改善 |

| 2009-12-08 00:00:00 | ノベラスシステムズジャパン ノベラスのPECVD ASHABLE HARD MASK (AHM(tm))がSub-32nmのパターニングを実現 従来のアモルファスカーボン膜に比べ歩留まりを7%改善 |